## P.5. Morphology Investigation of Gold Membranes Deposited by Electrochemical and Sputtering Techniques

Elena I. Monaico\*

National Center for Materials Study and Testing, Technical University of Moldova, Chisinau, Republic of Moldova

Email: elena.monaico@cnstm.utm.md

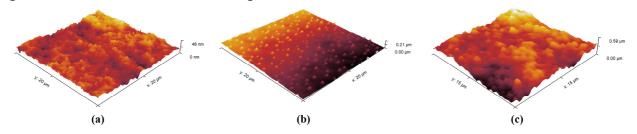

In this study, the morphology of gold layers deposited by pulsed electrochemical deposition on GaAs substrates was investigated using Atomic Force Microscopy (AFM). By adjusting the pulse duration, it was demonstrated that pores can be introduced in deposited Au layers [1]. According to previous studies, the deposition process follows the hopping electrodeposition mechanism [2,3]. For comparison, the study was also conducted on thin Au layers deposited by sputtering. The surface roughness of the bulk GaAs substrate, sputtered Au layer on GaAs, and Au layer deposited by pulsed electrochemical deposition on GaAs was determined to be 4 nm, 34 nm, and 65 nm, respectively. By reducing the pulse duration from 300 µs to 100 µs, it was demonstrated that the surface roughness of the Au film could be controlled, decreasing from 65 nm to 30 nm. Furthermore, during the anodization process of the GaAs substrate thought the Au film deposited by pulse electrochemical deposition, detachment of the gold membrane at an optimized anodization voltage was demonstrated. The ability to control the roughness of the Au films is significant for optimization of the materials performance in electronic and optoelectronic devices.

Figure 1. 3D AFM topology image of (a) bulk GaAs substrate; Au film deposited on bulk GaAs by sputtering (b) and (c) pulsed electrochemical deposition technique

## References:

- 1. Monaico, E.V.; Monaico, E.I.; Ursaki, V.V.; Tiginyanu, I.M. Free-Standing Large-Area Nanoperforated Gold Membranes Fabricated by Hopping Electrodeposition. *ECS J. Solid State Sci. Technol.* **2020**, *9*, 064010, doi:10.1149/2162-8777/aba6a2.

- 2. Tiginyanu, I.; Monaico, E.; Nielsch, K. Self-Assembled Monolayer of Au Nanodots Deposited on Porous Semiconductor Structures. *ECS Electrochem. Lett.* **2015**, *4*, D8, doi:10.1149/2.0041504eel.

- 3. Monaico, E.I.; Monaico, E.V.; Ursaki, V.V.; Tiginyanu, I.M. Controlled Electroplating of Noble Metals on III-V Semiconductor Nanotemplates Fabricated by Anodic Etching of Bulk Substrates. *Coatings* **2022**, *12*, 1521, doi:10.3390/coatings12101521.